지난글에서는 DRAM 성능을 발전시키기 위한 기술발전 중 커패시터에 관련된 내용을 살펴보았다.

2025.07.15 - [메모리 소자 이론] - DRAM의 전부 2편 (한계점, 기술 발전 - 커패시터 관련)

이번글에서는 DRAM 성능을 발전시키기 위한 기술발전 중 트랜지스터에 관련된 내용을 살펴보려고 한다.

트랜지스터 특성 개선

트랜지스터의 특성을 개선하여 누설전류를 최소화 하는 전략 또한 존재한다. 마찬가지로 cell 크기가 미세화 되면서 트랜지스터의 소스(Source)와 드레인(Drain) 사이 거리 (=Channel 길이) 또한 가까워지게 (짧아지게) 되었는데,

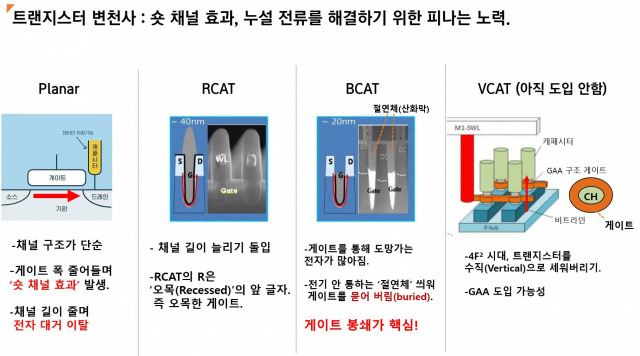

이에따라 게이트 전압 없이, 드레인에 가해지는 전압만으로도 전자가 흘러버리는 Short Channel Effect (SEC)이 발생하며 누설전류로 인한 다양한 문제점을 발생시켰다. 이 현상이 심해지면 Gate에 의해 On-Off 되는 Transistor 특성 자체를 잃을 수도 있다.

① RCAT과 SRCAT 구조

이를 해결하기 위한 대표적인 전략으로 Effective Channel Length(L)을 늘이는 전략이 있다.

이는 트랜지스터의 채널을 더 깊게 파서 U형이나 구형 구조로 만들어 파묻어 채널 길이를 연장하는 방법이다.

이러한 구조는 SCE를 억제하기 위해 소스와 드레인 사이의 길이(L)를 늘여주는 방법으로서

채널을 아래로 파고 게이트를 묻어 채널의 유효 길이 (Effective Length)를 길게 한다.

이를 적용한 구조에는 대표적으로 RCAT (Recessed Channel Array Transistor)가 있다.

S-RCAT 구조는, Sphere-RCAT 의 약자로, 기존 RCAT에서 나아가 채널 아랫쪽을 구 모양으로 추가적으로 에칭을 진행해 채널 길이를 더 길게 만들어준 구조다.

그러나 이런 구조들의 경우 Gate와 Drain이 인접하는 영역이 많아 GIDL (Gate Induced Drain Leakage) 현상이 발생할 수 있다. GIDL은 WL에 강한 음전압을 가하면 Drain으로누설전류가 흐르는 현상으로,

RCAT와 SRCAT의 경우 WL과 Drain이 이웃하는 영역이 넓기 때문에 GIDL 현상이 발생할 가능성이 크다.

② S - Fin 구조

이는 FinFET 구조와 (S)RCAT 구조를 같이 사용한 구조로,

RCAT의 장점으로 인해 effective channel length를 늘리면서도

Fin 구조의 장점으로 인해 Gate와 Oxide가 인접한 면적을 3면으로 늘려 gate 구동력 저하를 개선하여, 출력 특성을 향상 시킨 구조이다.

③ BCAT 구조

이를 해결하기 위해 더 발전시킨 구조에는 BCAT이 있다.

BCAT은 Buried Channel Array Transistor의 약자이다.

Buried라는 이름에서 알 수 있듯이,

S-Fin 구조에서 게이트를 기판 안에 아예 묻어버리고 Source와 Drain 사이는 절연체로 채우는 구조이다.

즉, RCAT과 달리 gate를 'U'자 구조의 하단에만 위치시키고 그 위에 산화막을 증착시켜 전기적으로 차단하는 방법이다.

이 기술을 적용하면 Gate와 Drain이 인접하는 영역을 최소화 할 수 있어 GIDL 현상을 해결할 수 있다.

또한 기존보다 bit line과 word line의 간격이 멀어지면서 배선간 short 이슈 또한 해결이 가능하다.

④ VCAT 구조

마지막으로는 VCAT (Vertical Channel Array Transistor)이라고 하는 차세대 구조이다.

이 구조는 게이트를 기둥 형태로 수직(vertical)으로 세우는 구조로, 트린지스터 구조인 Gate-all-around (GAA)를 수직형태로 만든다고 생각하면 된다.

이 구조를 적용할 경우, BCAT에서 달설한 6F² 배열에서 더 발전된 4F² 배열을 달성하여 밀집도를 더욱 높일 수 있게 된다.

그러나 현재 VCAT 구조는 Floating Body Effect (FBE)라는 난관을 완전히 해결하지 못해 아직 상용화 되지 않고 있다. 여러가지 연구가 활발하게 이루어지고 있으나, 아직 시뮬레이션/소자 단계/부분적 평가 단계에 그친 수준인듯 하다.

FBE란, 이러한 수직형태의 transistor에서 나타나는 문제점이다.

이러한 수직 구조에서 전자는 source에서 drain으로 원활하게 이동하지만, hole은 source와 gate 사이의 중립지역에 축적되게 된다.

이 축적된 hole에 의해 생긴 charge는 substrate에 양전압을 가하는 효과인 body effect를 유발해서 threshold voltage 변화, off-current 변화, noise 유발, transient 동작 불안정성 등 소자 특성을 저하 시킬 수 있는 것이다.

현재는 SOI (Silicon-On-Insulator) 및 Fully Depleted SOI (FD-SOI) 같은 기술을 활용하여 일부 해결하려는 다양한 시도가 이루어지고 있다.

결국, 가장 중요한 목표인

① 채널 길이 유지하면서 정전용량은 극대화

② 제한된 공간 내에 최대한 많은 셀 배치

를 달성하기 위한 기술 혁신의 여정인 것이다.

오류 및 기타 지적사항 환영

끝🍀

'메모리 소자 이론' 카테고리의 다른 글

| DRAM의 전부 2편 (한계점, 기술 발전 - 커패시터 관련) (0) | 2025.07.15 |

|---|---|

| DRAM의 전부 1편 (정의, 구조, 동작 원리, 특성 등) (0) | 2025.07.13 |