지난 글에서 기본적인 DRAM의 정의와 기본 구조, 동작 원리 등을 살펴보았다.

DRAM의 전부 1편 (정의, 구조, 동작 원리, 특성 등)

DRAM = Dynamic Random Access Memory의 약자이다. 메모리란 결국 정보를 저장하는 소자의 일종인데,이름의 뜻을 한번 살펴보자 ① DynamicDynamic RAM(DRAM)은 기본적으로 1개의 트랜지스터(Transistor)와 1개의 커

allgo77.tistory.com

이번편에서는 DRAM구조의 다양한 한계점과 차세대 DRAM으로 발전하기 위해 어떤 기술이 개선책으로 연구되었는지 자세하게 살펴보도록 하겠다.

DRAM의 커패시터에 저장한 전하는 지속적으로 충전하지 않으면 저장된 값을 유지하지 못하고 지속적으로 방전된다. 이렇게 손실된 전하를 보충하며 데이터를 유지시켜주기 위해 Refresh라는 전하 보충 과정을 주기적으로 해주어야 한다.

그러나,

이 과정 자체가 지속적으로 전력을 소모하며, Refresh 사이클 중간에는 데이터에 접근할 수가 없어 메모리의 성능을 저하시키게 된다.

즉, 커패시터의 누설전류를 줄이고 Refresh 주기를 길게 할수록 DRAM 성능을 개선할 수 있다.

물론, 트랜지스터 쪽에서의 누설전류를 줄임으로써도 DRAM 성능 개선이 가능하다.

즉, DRAM의 누설 전류를 최소화하기 위한 전략은 크게 커패시터(storage capacitor) 영역과 트랜지스터(access transistor) 영역으로 나눌 수 있다.

이번 편에서는 커패시터 관련 내용만 중점적으로 다뤄보겠다.

커패시터 특성 개선 (커패시턴스 증가 + 누설전류 방지)

커패시터에 Refresh 주기를 짧게하기 위해서 커패시터에 충분한 양의 전하를 저장하여 일정 수준 이상의 전하를 장시간 유지하도록 하는 전략이 있다.

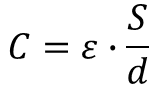

커패시턴스(C)는 다음과 같은 식으로 계산 되는데,

이때, S는 극판의 면적, d는 유전체 두께, ε는 유전체(dielectric)의 유전율(permittivity)임을 알고 있을 것이다.

즉, C 값을 크게 만드려면

1) 커패시턴스 형성 면적 S를 크게 만들거나

2) 유전체 두께 d를 얇게 만들거나

3) ε가 큰 물질(High-k dielectric)을 사용하면 되는 것이다.

그러나 최근 반도체 공정의 미세화가 진행되면서 셀 크기나 간격이 모두 작아지면서 최근 커패시턴스를 확보하기 위한 공간 및 구조에 큰 제약이 생기고 있다.

이에따라 터널링 등에 의해 발생하는 유전체 누설전류(dielectric leakge current) 또한 점차 증가하게 되어, 2) 유전체 두께 d를 일정 이상 얇게 제작하는 전략을 사용하기 어려워졌다.

따라서 제한된 공간에서 유전체 두께를 일정 이상 유지하면서도 1) 커패시턴스 형성 면적 S를 크게하기 위해, 커패시터의 구조는 평면(Planar)에서 입체 (3D-stacked) 구조로 발전해왔다.

하지만 셀 면적이 수 nm 수준으로 더더욱 줄어들면서 3D 기둥 모양의 캐패시터도 종횡비(Aspect Ratio)가 높아지며 지름이 줄어들고 길이가 점점 높아졌다. 최근 발전한 DRAM의 종횡비는 약 50:1 이상으로 알려져 있다!

과거에는 실린더형 커패시터 사이에 MESH라고 하는 지지대를 만들어 지탱하여 보완하였으나, 이후는 기둥(pillar) 형태의 커패시터로 발전하였으나 이 역시 구조적 안정성이 떨어져 커패시터가 쓰러지는 문제점은 여전히 존재하였다. 이를 해결하기 위해 지지대를 늘리고, 기둥을 2층 이상으로 나누어 쌓아 올리는 multi-pillar 구조 등으로 발전하였다.

무엇보다, 제한된 면적에서 일정 이상의 커패시턴스를 확보하기 위해 3) 높은 유전율을 가진 High-k 물질을 사용하기 위한 연구 또한 지속되어 왔다.

유전율이란 물체에 전기장이 인가될 때, 전하를 얼마나 잘 잡아두는지를 나타내는 척도이다. 따라서 High-k 소재는 고유전율 소재로 같은 전압을 인가하더라도 다른 소재보다 더 전하를 잡아둘 수 있기 때문에 커패시턴스 또한 증가한다.

이에 따라 유전막 소재는 아래처럼 발전해 왔으며, 최근까지 20~25 정도의 유전율을 갖는 하프늄옥사이드(HfO₂) 또는 20~30의 유전율을 갖는 지르코늄 옥사이드(ZrO₂)를 사용하는 형태로 바뀌어 왔다.

SiO₂ → ONO → Al₂O₃ → HfO₂ → ZrO₂

(참고 : ONO란 Oxide/Nitride/Oxide의 여러층으로 이루어진 절연막, 1차 산화막+질화막+2차 산화막을 말한다)

그렇다면 왜 약 60~80의 매우 높은 유전율을 갖는 티타늄옥사이드(TiO₂)를 유전막 소재로 사용하지 않을까? 그 이유는 ① 물체의 밴드갭(Bandgap)에 따른 누설전류와의 관계 및 ② 커패시터의 충/방전 시간에 있다.

SiO₂ 는 3.9의 낮은 유전상수를 갖지만, 약 9.1eV의 높은 밴드갭을 가지고 있어 우수한 절연 특성을 가지고 있다. 하지만 TiO₂는 3.05eV의 낮은 밴드갭을 가지고 있어 dielectric layer로 사용할 경우 누설전류가 크게 증가할 가능성이 있는 것이다. 일반적으로, 유전상수 k가 높을수록 밴드갭은 낮아지는 반비례의 경향이 존재한다.

또한, 커패시턴스가 너무 크면 커패시터를 충/방전하는 시간이 길어지기 때문에 DRAM의 동작속도가 저하된다는 가능성도 있다.

그래서 이러한 trade-off 관계를 고려하여 현재는 20~25의 높은 유전율과 5~7eV의 적절한 Energy bandgap을 갖는 HfO₂ 또는 ZrO₂ 가 High-k 소재로 사용되었다.

일반적으로 단일 물질만을 사용하는 것이 아닌, ZrO₂ /Al₂O₃ /ZrO₂ (ZAZ)처럼 다양한 물질들을 다층으로 적층하여 사용하거나

(High-k 유전체 + 넓은 밴드갭 갖는 blocking layer 조합)

도핑이나 결정구조 엔지니어링을 통한 박막 특성 최적화를 진행하여 사용하고 있다.

(Al-doped TiO₂ (ATO), SrTiO₃ (STO) 등 연구 중)

당연히 박막의 품질과 균일도, Step Coverage 또한 매우 중요하기 때문에 (PE)ALD등의 공정이 이러한 dielectric 물질을 증착하기 위해 사용되고 있다.

오류 및 기타 지적사항 환영

3편에서 계속🍀

'메모리 소자 이론' 카테고리의 다른 글

| DRAM의 전부 3편 (한계점 및 기술 발전-트랜지스터 관련) (1) | 2025.07.17 |

|---|---|

| DRAM의 전부 1편 (정의, 구조, 동작 원리, 특성 등) (0) | 2025.07.13 |